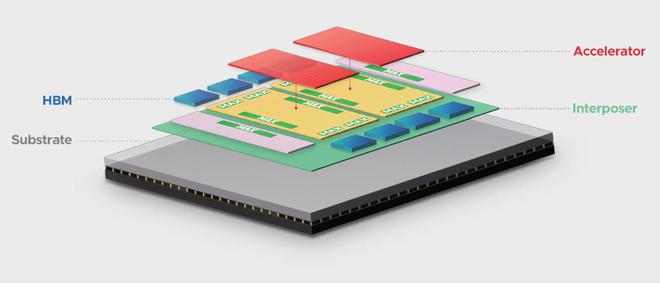

12 月 6 日消息,博通当地时间昨日宣布推出行业首个 3.5D F2F 封装技术 3.5D XDSiP 平台。3.5D XDSiP 可在单一封装中集成超过 6000mm2 的硅芯片和多达 12 个 HBM 内存堆栈,可满足大型 AI 芯片对高性能低功耗的需求。

射频微波器件采购网(www.ic-king.com)专注整合国内外厂商的现货渠道,实时查询射频微波器件代理商的真实库存,提供合理的行业价格,放心采购射频微波器件,是国内专业的射频微波芯片采购平台。

具体来看,博通的 3.5D XDSiP 在 2.5D 封装之外还实现了上下两层芯片顶部金属层的直接连接(即 3D 混合铜键合),同时具有最小的电气干扰和卓越的机械强度。

这一“面对面”的连接方式相比传统“面对背”式芯片垂直堆叠拥有 7 倍的信号密度,最大限度减少了 3D 芯片堆栈中各组件间的延迟,相较平面芯片间 PHY 接口功耗大幅降低九成,实现了更小的中介层和封装尺寸,从而在节省成本的同时还改善了大面积封装的翘曲问题。

博通公司高级副总裁兼 ASIC 产品部总经理 Frank Ostojic 表示:

先进的封装对于下一代 XPU 集群至关重要,因为我们已经达到了摩尔定律的极限。 通过与客户密切合作,我们在台积电和 EDA 合作伙伴的技术和工具基础上创建了 3.5D XDSiP 平台。 通过垂直堆叠芯片元件,博通的 3.5D 平台使芯片设计人员能够为每个元件搭配合适的制造工艺,同时缩小中介层和封装尺寸,从而显著提高性能、效率和成本。

台积电业务开发、全球业务资深副总经理兼副共同营运长张晓强表示:

在过去几年中,台积电与博通紧密合作,将台积电最先进的逻辑制程和 3D 芯片堆叠技术与博通的设计专长相结合。 我们期待着将这一平台产品化,以实现 AATOP代理I 创新和未来增长。

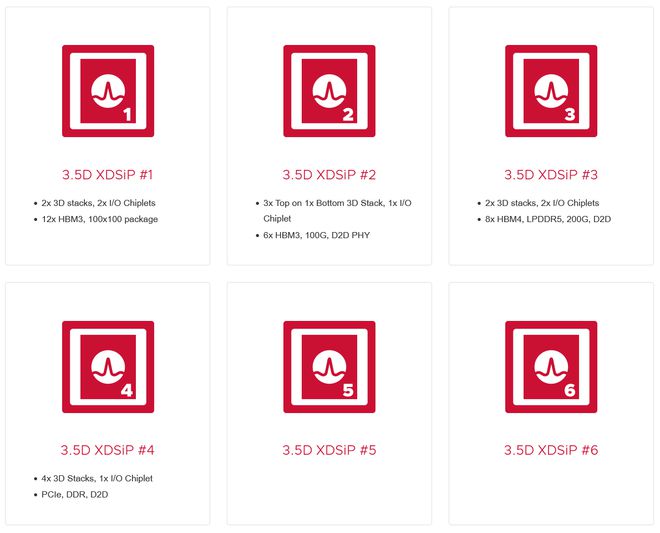

博通表示,其大多数“消费级 AI 客户”已采用3.5D XDSiP 平台技术,正在开发的 3.5D 产品已达 6 款,将于 2026 年 2 月开始生产出货。其中富士通已明确将在其 2nm 制程 Arm 服务器处理器 FUJITSU-MONAKA 使用这一平台。

▲ 博通官网展示的六个 3.5D XDSiP 案例富士通的 FUJITSU-MONAKA 应该对应 #4

- 英伟达助攻人形机器人!Jetson Thor 芯片量产,产业 “奇点” 临近

- 求变!三星将全面整顿封装供应链:材料设备采购规则全改,供应链调整

- 英伟达携手台积电押注硅光子学,共筑 AI 芯片新高度,引领技术潮流

- Arm 芯片涨价 300%:完整设计方案 或影响安卓阵营

- 英特尔整合 ASML High-NA EUV 光刻设备,加速半导体制造技术升级

- ADI CodeFusion Studio 升级!加速产品开发 + 数据安全,漏洞检测率达 99.9%

- 研华工业主板 AIMB-289 火力全开,精准赋能内窥镜性能飞跃,全力助推智慧医疗迈向新高度

- 亚马逊打响 AI 军备竞赛!自研芯片阵列 + 大模型,英伟达王座岌岌可危

- 英特尔持续依赖台积电!18A 工艺提升难改代工依赖,本土产能不足

- 国产 AI 芯片巨头风云突变,寒武纪被前 CTO 索赔 42.9 亿股权激励

- 美国确保芯片本土生产!英特尔暴涨 6%,18A 制程产能规划曝光

- 安森美收购碳化硅 JFET,AI 数据中心电源升级,服务器能效比提升 20%

嵌入式 - FPGA(现场可编程门阵列)

嵌入式 - FPGA(现场可编程门阵列) RF 天线(射频和无线)

RF 天线(射频和无线) 温度传感器 > 模拟和数字输出 - 工业(传感器,变送器)

温度传感器 > 模拟和数字输出 - 工业(传感器,变送器) 评估板 > 嵌入式 MCU、DSP 评估板(开发板,套件,编程器)

评估板 > 嵌入式 MCU、DSP 评估板(开发板,套件,编程器) 衰减器(射频和无线)

衰减器(射频和无线) 射频收发器模块和调制解调器(射频和无线)

射频收发器模块和调制解调器(射频和无线) 电流传感器(传感器,变送器)

电流传感器(传感器,变送器) 同轴连接器(射频) > 同轴连接器(RF)适配器(连接器,互连器件)

同轴连接器(射频) > 同轴连接器(RF)适配器(连接器,互连器件) 射频放大器(射频和无线)

射频放大器(射频和无线) 接近传感器 - 工业(传感器,变送器)

接近传感器 - 工业(传感器,变送器) 端子块 > 接口模块(连接器,互连器件)

端子块 > 接口模块(连接器,互连器件) 流量传感器(传感器,变送器)

流量传感器(传感器,变送器)